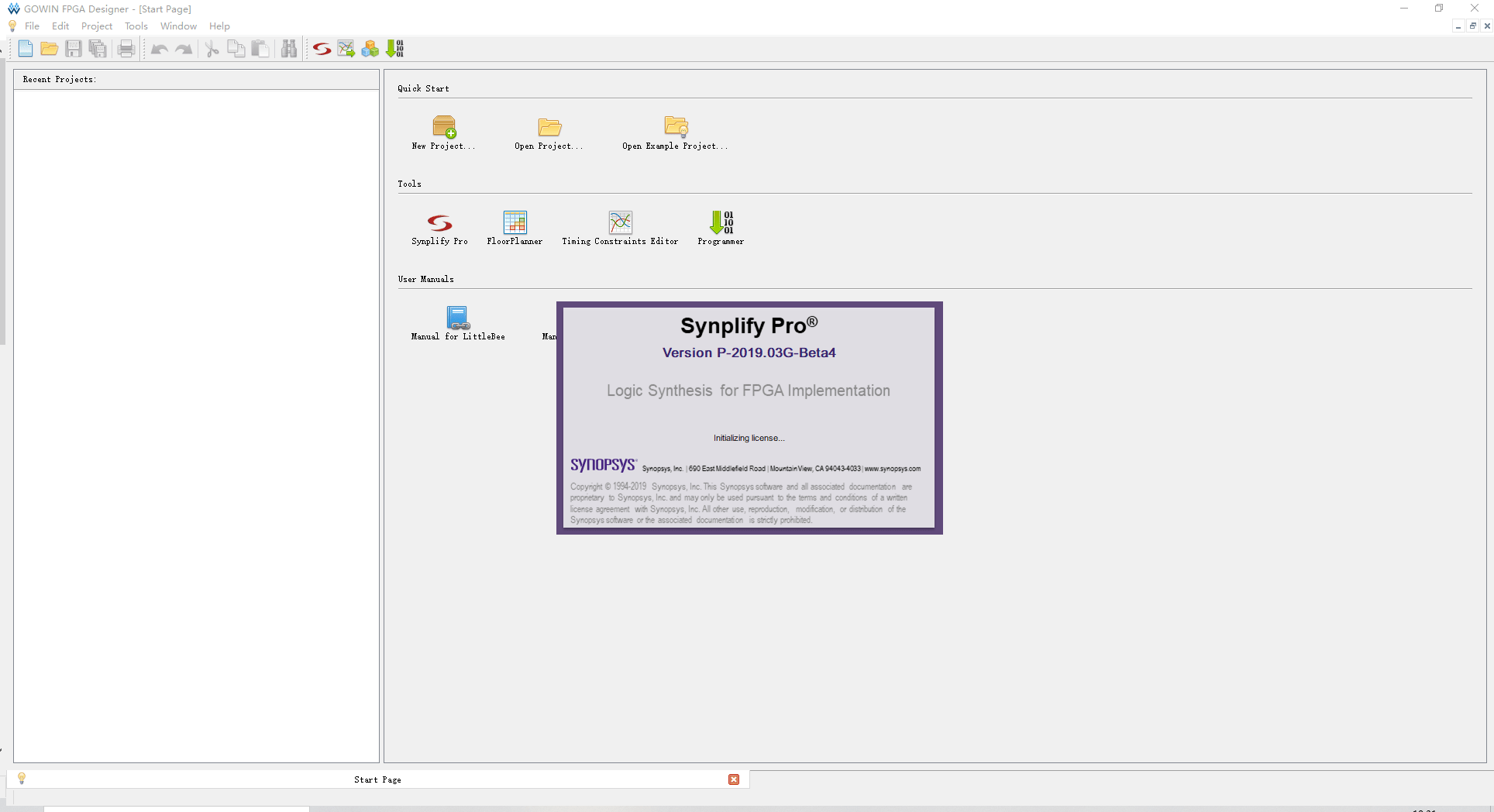

Graph-Based Physical Synthesis Invented by Synplicity, graph-based physical synthesis improves timing closure by means of a single-pass physical synthesis flow for 90nm FPGAs. To determine whether your operating system requires patches, refer to the following procedure. The Synplify Premier software dramatically accelerates the debug process and provides a rapid and incremental method for finding elusive design problems. Linux (x86圆4): Red Hat Enterprise Linux 4/5/6 (32/64-bit) Required Operating System Patches Running this software requires that the Linux operating system include specific patches. In addition, the Synplify Premier product offers FPGA Designers and ASIC Prototypers the most efficient method of in-system verification of FPGAs. The highly accurate correlation between the Synplify Premier product’s timing estimates and final design timing enables more aggressive optimization resulting in improved device performance. The Synplify Premier tool’s graph-based physical synthesis technology addresses timing closure by merging optimization, placement, routing and generates a fully placed and physically optimized design ready for final routing using the FPGA vendor routing tool. We provide cracked softwares, these software are all in english language and. It builds upon Synplicity’s industry-leading synthesis technology by adding graph-based physical synthesis and real-time simulator-like visibility into operating FPGA devices.

Synplicity’s Synplify Premier Linux software is the ultimate FPGA timing closure and debug solution.

0 kommentar(er)

0 kommentar(er)